## **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

## A REPORT ON UNIVERSAL VERIFICATION METHODOLOGY WORKSHOP

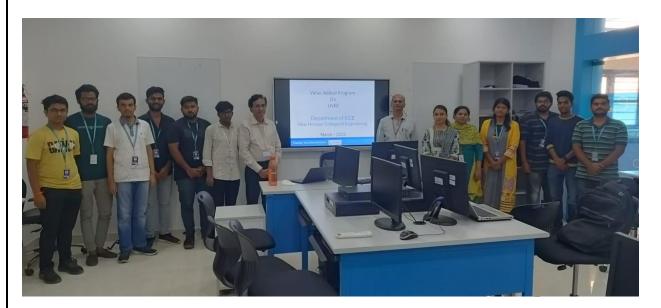

Date Duration Workshop topic Number of Participants :24-04-2023 :4 hours :Universal Verification Methodology :41

The comprehensive VLSI workshop not only provided students with theoretical insights but also focused on the practical application of knowledge gained from UVM classes. Through hands-on experience in designing a 16-bit ALU using Verilog, participants honed their skills in hardware description languages and gained a profound understanding of the intricacies involved in creating complex digital circuits. The project implementation phase challenged students to optimize the ALU for speed while minimizing resource utilization, fostering a deep appreciation for the delicate balance between performance and efficiency in VLSI design. The UVM proficiency attained during the workshop was instrumental in creating a structured verification environment for the ALU project, ensuring the reliability and robustness of the implemented designs. Debugging complex Verilog code presented students with real-world scenarios, allowing them to refine their problem-solving skills and reinforcing the importance of thorough testing in the VLSI design process.

The workshop's success in providing a holistic understanding of the entire VLSI design flow was evident as students navigated through the stages of translating functional specifications into Verilog code, synthesizing their designs, and finally, validating the functionality through simulations. The collaborative nature of the project work encouraged teamwork, communication, and sharing of best practices among participants. Looking forward, future iterations of the workshop could incorporate more advanced ALU designs, exploring emerging technologies and trends in VLSI. Additionally, a focus on industry-relevant applications and real-world case studies could further enhance the practical applicability of the skills acquired. Continuing to expand the UVM curriculum to cover advanced verification techniques and methodologies would ensure that students are well-prepared to address the evolving challenges in VLSI design.

In conclusion, the VLSI workshop not only equipped students with the technical skills required for ALU design and Verilog coding but also instilled a mindset of adaptability and problem-solving crucial for success in the dynamic field of VLSI. The integration of UVM classes and practical project work created a well-rounded learning

experience, preparing students to contribute effectively to the ever-evolving landscape of semiconductor and chip design.