FDP

ASIC Design Flow using Mentor Graphics

Date: 26/01/2022

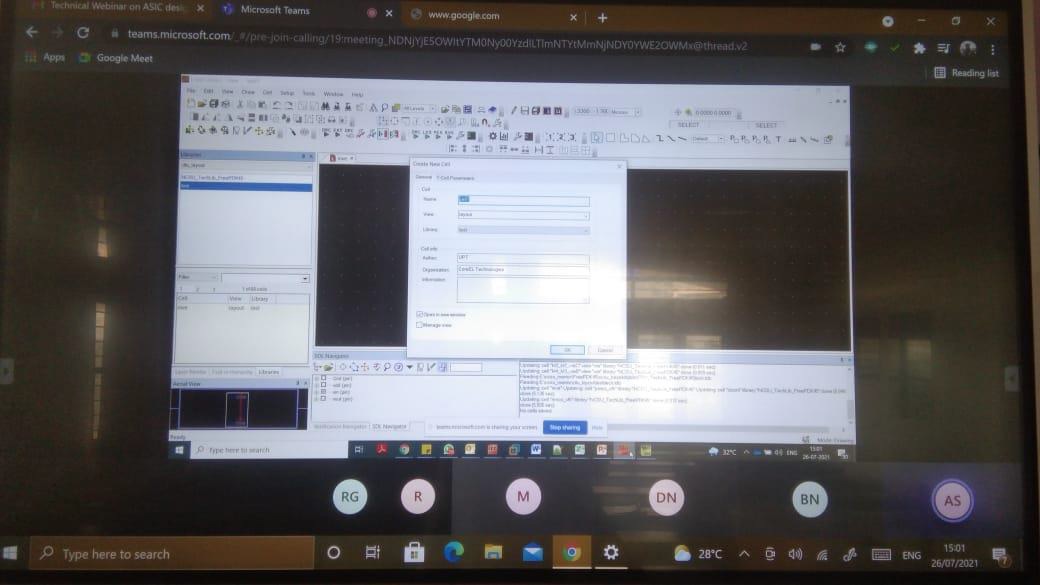

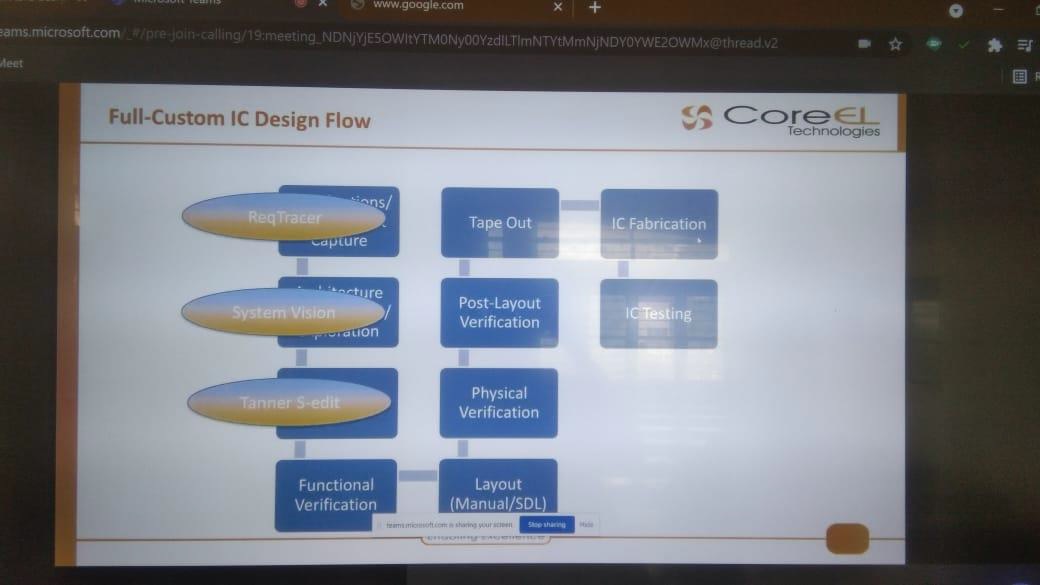

Industrial Training Program for Faculty on ASIC Design Flow using Mentor Graphics in association with CoreEL Technologies was conducted on 26th July, 2021. The Session was delivered by Mr. Ankur Sangal Senior Application Engineer, CoreEL Technologies Bangalore and supported by Bhanu Prakash Dixith B N Associate Manager – University Relations CoreEL Technologies Bangalore. Dr.P.Piruthiviraj , Associate Professor /ECE is the faculty coordinator of the Program. During the session, the speaker has covered the Session on Full custom and Semi Custom Design. Faculties from Department of ECE have participated in this training program. Thereafter VLSI software demonstration is delivered as a Hands-on Session.

Outcome of the Industrial Training/FDP:

• EDA tool flow eliminates time consuming aspects of mixed signal development like polygon editing and layout verification.

• In view to provide a better exposure for the faculty and students in the Design and Verification of Digital Circuits using front-end and back-end tools the industrial training program has been designed.

• This training has given an invaluable resource for the participants, those who are trying to enhance their knowledge in the current needs of the VLSI Industry.